3.10: Рівні напруги логічного сигналу

- Page ID

- 101137

Схеми логічних затворів призначені для введення і виведення тільки двох типів сигналів: «високий» (1) і «низький» (0), як представлений змінною напругою: повна напруга живлення для «високого» стану і нульова напруга для «низького» стану. У ідеальному світі всі сигнали логічної схеми існували б на цих граничних границях напруги і ніколи не відхилялися від них (тобто менше повної напруги для «високої», або більше нульової напруги для «низької»). Однак насправді рівні напруги логічного сигналу рідко досягають цих ідеальних меж через бродячі падіння напруги в транзисторній схемі, і тому ми повинні розуміти обмеження рівня сигналу ланцюгів затвора, коли вони намагаються інтерпретувати напруги сигналу, що лежать десь між повною напругою живлення і нуль.

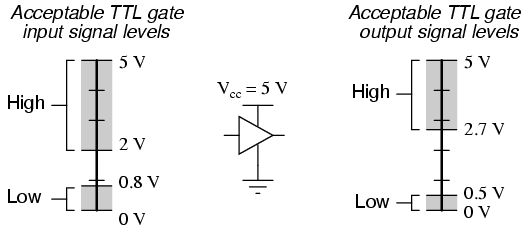

TTL ворота працюють від номінальної напруги живлення 5 вольт, +/- 0,25 вольт. В ідеалі, TTL «високий» сигнал буде точно 5.00 вольт, а TTL «низький» сигнал 0.00 вольт точно. Однак справжні схеми затвора TTL не можуть виводити такі ідеальні рівні напруги, і призначені для прийняття «високих» і «низьких» сигналів, що істотно відхиляються від цих ідеальних значень. «Прийнятні» напруги вхідного сигналу варіюються від 0 вольт до 0,8 вольт для «низького» логічного стану та від 2 вольт до 5 вольт для «високого» логічного стану. «Прийнятні» напруги вихідного сигналу (рівні напруги, гарантовані виробником затвора в заданому діапазоні умов навантаження) варіюються від 0 вольт до 0,5 вольт для «низького» логічного стану і 2,7 вольт до 5 вольт для «високого» логічного стану:

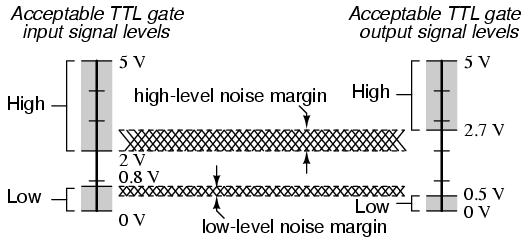

Якби сигнал напруги в діапазоні від 0,8 вольт до 2 вольт повинен був бути відправлений на вхід затвора TTL, певної реакції від затвора не було б. Такий сигнал буде вважатися невизначеним, і жоден виробник логічних воріт не гарантує, як їх схема затвора буде інтерпретувати такий сигнал.

Як бачите, допустимі діапазони для рівнів вихідного сигналу вужчі, ніж для рівнів вхідного сигналу, щоб гарантувати, що будь-який затвор TTL, що виводить цифровий сигнал на вхід іншого затвора TTL, буде передавати напруги, прийнятні для приймального затвора. Різниця між допустимим вихідним і вхідним діапазонами називається шумовим запасом затвора. Для затворів TTL низький рівень шуму - це різниця між 0,8 вольт і 0,5 вольта (0,3 вольта), тоді як рівень шуму - це різниця між 2,7 вольтами і 2 вольтами (0,7 вольта). Простіше кажучи, запас шуму - це пікова кількість помилкової або «шумової» напруги, яка може бути накладена на слабкий сигнал вихідної напруги затвора, перш ніж приймальний затвор може неправильно інтерпретувати його:

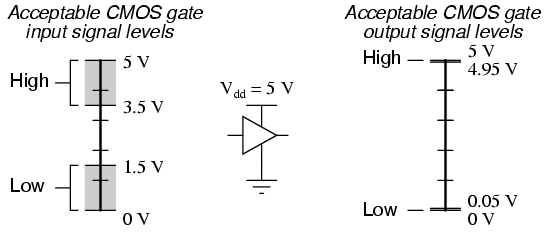

Схеми затвора CMOS мають характеристики вхідного та вихідного сигналу, які сильно відрізняються від TTL. Для CMOS затвора, що працює при напрузі живлення 5 вольт, допустимі напруги вхідного сигналу коливаються від 0 вольт до 1,5 вольт для «низького» логічного стану і 3,5 вольт до 5 вольт для «високого» логічного стану. «Прийнятні» напруги вихідного сигналу (рівні напруги, гарантовані виробником затвора в заданому діапазоні умов навантаження) варіюються від 0 вольт до 0,05 вольт для «низького» логічного стану і 4,95 вольт до 5 вольт для «високого» логічного стану:

З цих цифр повинно бути очевидно, що схеми затвора CMOS мають набагато більшу межу шуму, ніж TTL: 1,45 вольта для CMOS низького рівня та високого рівня, проти максимум 0,7 вольт для TTL. Іншими словами, схеми CMOS можуть переносити більш ніж удвічі більшу кількість накладеної «шумової» напруги на своїх вхідних лініях, перш ніж призведе до помилок інтерпретації сигналу.

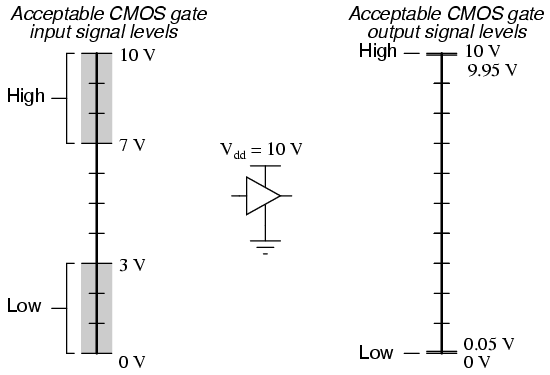

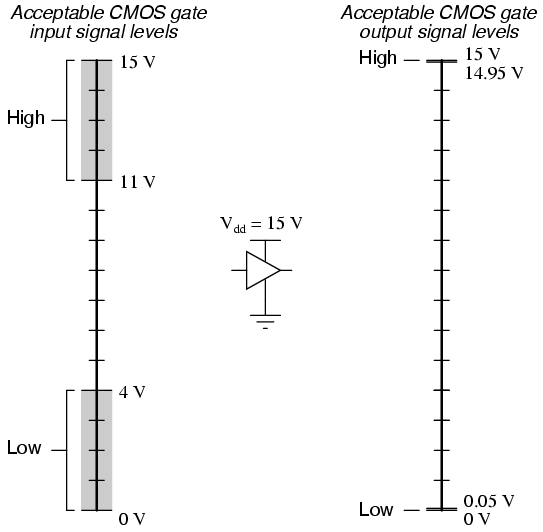

Поля шуму CMOS розширюється ще більше з більш високими робочими напругами. На відміну від TTL, який обмежений напругою живлення 5 вольт, CMOS може харчуватися від напруги до 15 вольт (деякі схеми CMOS до 18 вольт). Тут показані прийнятні «високий» і «низький» стани, як для входу, так і для виходу, інтегральних мікросхем CMOS, що працюють на 10 вольт і 15 вольт відповідно:

Поля для прийнятних сигналів «високого» і «низького» може бути більше, ніж показано на попередніх ілюстраціях. Те, що показано, являє собою «найгірший випадок» продуктивність вхідного сигналу, виходячи зі специфікацій виробника. На практиці можна виявити, що схема затвора буде переносити «високі» сигнали значно меншої напруги та «низькі» сигнали значно більшої напруги, ніж зазначені тут.

І навпаки, показані надзвичайно малі вихідні поля - гарантуючи вихідні стани для «високих» та «низьких» сигналів до 0,05 вольт від «рейок» джерела живлення - оптимістичні. Такі «солідні» рівні вихідної напруги будуть вірні тільки для умов мінімального навантаження. Якщо затвор джерела або занурення значного струму до навантаження, вихідна напруга не зможе підтримувати ці оптимальні рівні, через внутрішній опір каналу кінцевого виходу MOSFET затвора.

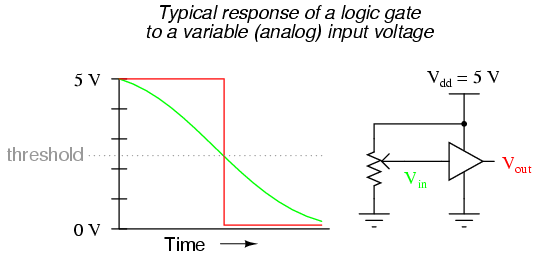

У межах «невизначеного» діапазону для будь-якого входу воріт буде певна точка розмежування, що розділяє фактичний «низький» діапазон вхідного сигналу воріт від його фактичного «високого» діапазону вхідного сигналу. Тобто десь між найнижчим «високим» рівнем напруги сигналу і найвищим «низьким» рівнем напруги сигналу, гарантованим виробником затвора, існує порогове напруга, при якому затвор фактично перемикає свою інтерпретацію сигналу з «низького» або «високого» або навпаки. Для більшості ланцюгів затвора це невизначене напруга є єдиною точкою:

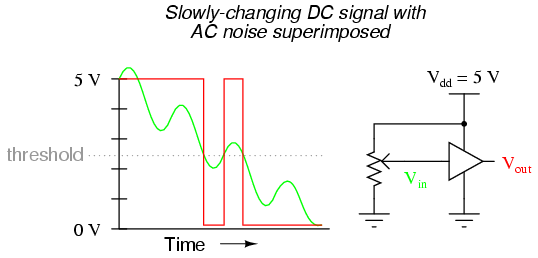

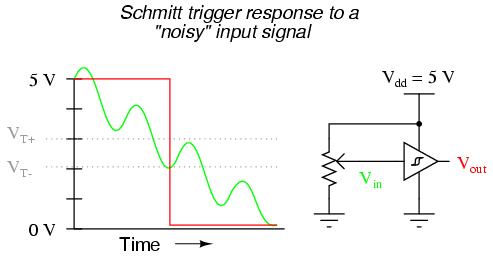

При наявності змінного «шумового» напруги, накладеного на вхідний сигнал постійного струму, єдина порогова точка, при якій затвор змінює свою інтерпретацію логічного рівня, призведе до нестабільного виходу:

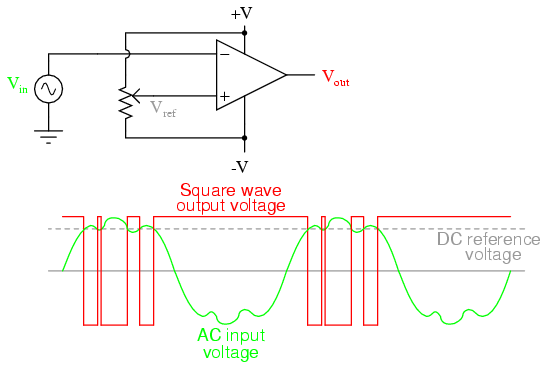

Якщо цей сценарій виглядає вам знайомим, це тому, що ви пам'ятаєте подібну проблему з (аналоговими) схемами операційних підсилювачів напруги. При єдиній пороговій точці, в якій вхід змушує вихід перемикатися між «високим» і «низьким» станами, наявність значних шумів спричинить нестабільні зміни на виході:

Рішенням цієї проблеми є трохи позитивних відгуків, внесених в схему підсилювача. За допомогою операційного підсилювача це робиться шляхом підключення виходу назад до неінвертирующего (+) входу через резистор. У схемі затвора це тягне за собою перепланування внутрішньої схеми затвора, встановлення зворотного зв'язку всередині пакета воріт, а не через зовнішні з'єднання. Затвор, розроблений таким чином, називається спусковим гачком Шмітта. Тригери Шмітта інтерпретують змінну вхідну напругу відповідно до двох порогових напруг: позитивного порогу (V T +) та негативного порогу (V T-):

Пускові затвори Шмітта відрізняються на принципових схемах малим символом «гістерезису», намальованим всередині них, що нагадує криву B-H для феромагнітного матеріалу. Гістерезис, породжений позитивним зворотним зв'язком у схемі затвора, додає додатковий рівень завадостійкості до продуктивності затвора. Тригерні ворота Шмітта часто використовуються в додатках, де очікується шум на лінії вхідного сигналу та/або де непостійний вихід буде дуже шкідливим для продуктивності системи.

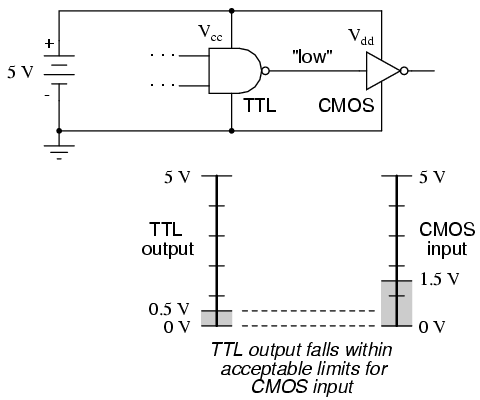

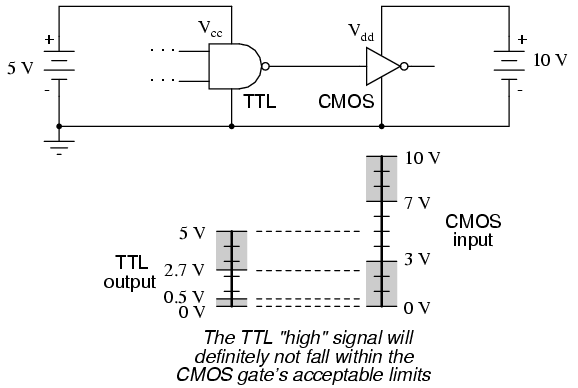

Різні вимоги до рівня напруги TTL та CMOS технології створюють проблеми, коли два типи воріт використовуються в одній системі. Незважаючи на те, що робота CMOS затворів на тій же напрузі живлення 5.00 вольт, необхідна для воріт TTL, не є проблемою, рівні вихідної напруги TTL не будуть сумісні з вимогами до вхідної напруги CMOS.

Візьмемо, наприклад, TTL NAND затвор, що виводить сигнал на вхід затвора інвертора CMOS. Обидва затвори харчуються від одного і того ж джерела живлення 5.00 вольт (V cc). Якщо затвор TTL видає «низький» сигнал (гарантовано становить від 0 вольт до 0,5 вольт), він буде правильно інтерпретований входом CMOS затвора як «низький» (очікуючи напруги від 0 вольт до 1,5 вольт):

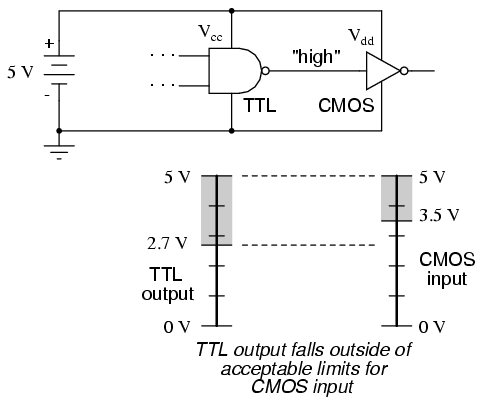

Однак, якщо затвор TTL видає «високий» сигнал (гарантовано становить від 5 вольт до 2.7 вольт), він може не бути належним чином інтерпретований входом CMOS як «високий» (очікуючи напруги від 5 вольт до 3,5 вольт):

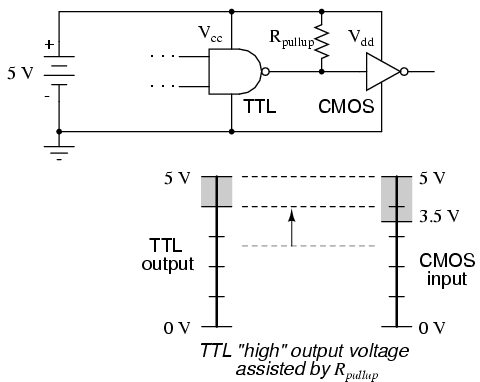

Враховуючи цю невідповідність, затвор TTL цілком можливо вивести дійсний «високий» сигнал (дійсний, тобто відповідно до стандартів для TTL), який знаходиться в межах «невизначеного» діапазону для входу CMOS, і може бути (помилково) інтерпретований як «низький» приймальним затвором. Просте «виправлення» цієї проблеми полягає в тому, щоб збільшити «високий» рівень напруги сигналу TTL затвора за допомогою тягового резистора:

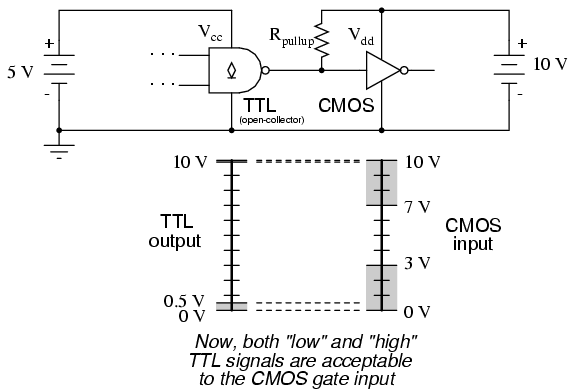

Щось більше, ніж це, потрібно для інтерфейсу виходу TTL з входом CMOS, якщо приймаючий CMOS затвор живиться від більшої напруги живлення:

Звичайно, не буде проблем з CMOS затвором інтерпретації «низького» виходу TTL затвора, але «високий» сигнал від затвора TTL зовсім інша справа. Гарантований діапазон вихідної напруги від 2,7 вольт до 5 вольт від виходу затвора TTL ніде не знаходиться поблизу прийнятного діапазону CMOS затвора від 7 вольт до 10 вольт для «високого» сигналу. Якщо ми використовуємо затвор TTL з відкритим колектором замість вихідного затвора тотем-полюса, хоча, підтягуючий резистор до шини живлення 10 вольт V dd підніме «високу» вихідну напругу затвора TTL до повної напруги живлення, що подає затвор CMOS. Так як затвор з відкритим колектором може топити тільки струм, а не джерело струму, то «високий» рівень напруги стану цілком визначається джерелом живлення, до якого приєднаний тягне резистор, таким чином акуратно вирішуючи проблему невідповідності:

Завдяки відмінним характеристикам вихідної напруги CMOS затворів, як правило, немає проблем з підключенням виходу CMOS до входу TTL. Єдиною суттєвою проблемою є поточне навантаження, представлене входами TTL, оскільки вихід CMOS повинен занурювати струм для кожного з входів TTL, перебуваючи в «низькому» стані.

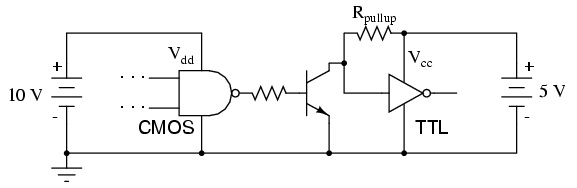

Коли CMOS затвор, про який йде мова, живиться від джерела напруги понад 5 вольт (V cc), однак, проблема призведе до виникнення. «Високий» вихідний стан затвора CMOS, що перевищує 5 вольт, перевищить прийнятні вхідні межі TTL затвора для «високого» сигналу. Рішенням цієї проблеми є створення схеми інвертора «відкритого колектора» за допомогою дискретного NPN-транзистора, і використання його для сполучення двох воріт разом:

Резистор «R pullup» є необов'язковим, оскільки входи TTL автоматично припускають «високий» стан, коли лівий плаваючий, що станеться, коли вихід затвора CMOS «низький», а транзистор відсікає. Звичайно, одним дуже важливим наслідком реалізації цього рішення є логічна інверсія, створена транзистором: коли CMOS затвор видає «низький» сигнал, затвор TTL бачить «високий» вхід; а коли CMOS затвор видає «високий» сигнал, транзистор насичується і затвор TTL бачить «низький» вхід. Поки ця інверсія врахована в логічній схемі системи, все буде добре.