3.7: Схема затвора CMOS

- Page ID

- 101130

До цього моменту наш аналіз логічних схем транзисторів обмежувався парадигмою дизайну TTL, за допомогою якої використовуються біполярні транзистори, а загальна стратегія плаваючих входів еквівалентна «високим» (підключеним до V cc) входів - і відповідно, припуску «відкритого» -колектор» вихідні етапи — підтримується. Це, однак, не єдиний спосіб побудувати логічні ворота.

Польові транзистори

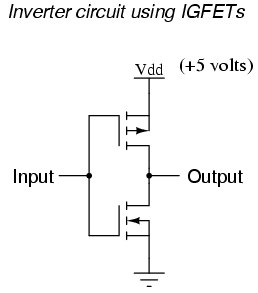

Польові транзистори, особливо різновид ізольованих затворів, можуть бути використані при проектуванні ланцюгів затвора. Будучи контрольованими напругою, а не пристроями, керованими струмом, IGFET, як правило, дозволяють дуже прості конструкції схем. Візьмемо, наприклад, наступну схему інвертора, побудовану з використанням P- та N-канальних IGFET:

Зверніть увагу на ярлик «V dd» на позитивному клемі джерела живлення. Ця мітка дотримується тієї ж конвенції, що і «V cc» в схемах TTL: це означає постійну напругу, прикладену до стоку польового транзистора, стосовно землі.

Польові транзистори в ланцюгах затвора

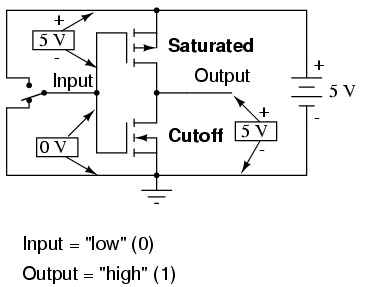

Давайте підключимо цю схему затвора до джерела живлення і вхідного вимикача, і вивчимо його роботу. Будь ласка, зверніть увагу, що ці IGFET транзистори є E-типу (Enhancement-режим), і так це нормально вимкнені пристрої. Він приймає прикладену напругу між затвором і стоком (власне, між затвором і підкладкою) правильної полярності, щоб змістити їх.

Верхній транзистор - це P-канал IGFET. Коли канал (підкладка) зроблений більш позитивним, ніж затвор (затвор негативний щодо підкладки), канал посилюється і допускається струм між джерелом і стоком. Отже, на наведеній вище ілюстрації включений верхній транзистор.

Нижній транзистор, що має нульову напругу між затвором і підкладкою (джерелом), знаходиться в нормальному режимі: вимкнено. Таким чином, дія цих двох транзисторів таке, що вихідний затвор ланцюга затвора має міцне з'єднання з V dd і дуже високий опір з'єднання з землею. Це робить висновок «high» (1) для «низького» (0) стану вхідних даних.

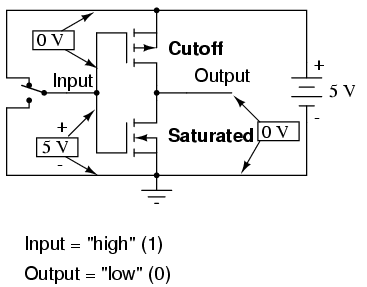

Далі переведемо вхідний перемикач в інше положення і подивимося, що вийде:

Тепер нижній транзистор (N-канал) насичений, оскільки він має достатню напругу правильної полярності, прикладеної між затвором і підкладкою (каналом) для його включення (позитивне на затворі, негативне на каналі). Верхній транзистор, що має нульову напругу, що подається між його затвором і підкладкою, знаходиться в нормальному режимі: вимкнений. Таким чином, вихід цієї схеми затвора тепер «низький» (0). Зрозуміло, що ця схема демонструє поведінку інвертора, або НЕ затвора.

Додаткові напівпровідники з оксиду металу (CMOS)

Використання польових транзисторів замість біполярних транзисторів значно спростило конструкцію затвора інвертора. Зверніть увагу, що вихід цього затвора ніколи не плаває, як у випадку з найпростішою схемою TTL: він має природну конфігурацію «тотем-полюс», здатну як джерело, так і потоковий струм навантаження. Ключем до елегантного дизайну цієї схеми воріт є додаткове використання як P-, так і N-канальних IGFET. Оскільки IgFET більш відомі як МОП-транзистори (M метал-O оксид-S напівпровідник F поле Е ефект T транзистор), і в цій схемі використовуються як P-, так і N- канальні транзистори разом, загальна класифікація, дана ланцюгам затвора, як ця, є CMOS: C комплементарний M метал O оксид S напівпровідник.

CMOS Gates: виклики та рішення

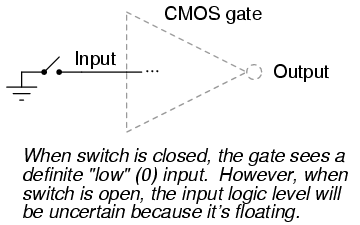

Схеми CMOS не страждає від властивих нелінійностей польових транзисторів, оскільки, як цифрові схеми, їх транзистори завжди працюють в режимах насичення або відсічення і ніколи не в активному режимі. Однак їх входи чутливі до високих напруг, що генеруються електростатичними (статичною електрикою) джерел, і навіть можуть бути активовані в «високий» (1) або «низький» (0) стани паразитними джерелами напруги, якщо вони залишаються плаваючими. З цієї причини недоцільно дозволяти вхід логічного затвора CMOS плавати за будь-яких обставин. Будь ласка, зверніть увагу, що це дуже відрізняється від поведінки шлюзу TTL, де плаваючий вхід був безпечно інтерпретований як «високий» (1) логічний рівень.

Це може спричинити проблему, якщо вхід до логічного затвора CMOS приводиться в дію одним кидком перемикача, де один стан має вхід міцно підключений або до V dd або землі, а інший стан має вхід плаваючий (ні до чого не підключений):

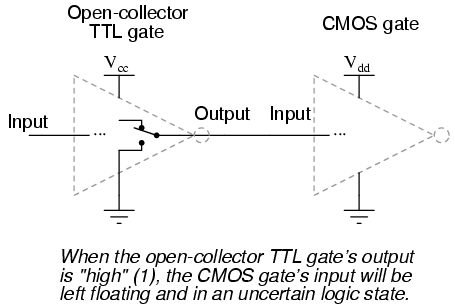

Також ця проблема виникає в тому випадку, якщо вхід затвора CMOS приводиться в рух затвором TTL з відкритим колектором. Оскільки такий вихід TTL затвора плаває, коли він йде «високим» (1), вхід CMOS затвора залишиться в невизначеному стані:

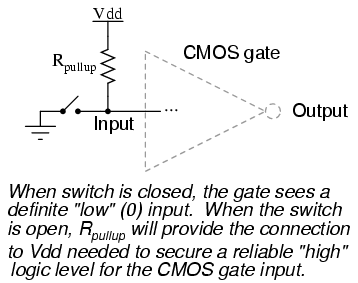

На щастя, існує просте рішення цієї дилеми, яке часто використовується в логічних схемах CMOS. Всякий раз, коли перемикач з одним кидком (або будь-який інший вид виходу затвора, не здатний як джерела, так і потоковий струм) використовується для приводу входу CMOS, резистор, підключений або до V dd або землі, може бути використаний для забезпечення стабільного логічного рівня для стану, в якому приводний пристрій вихід плаваючий. Значення цього резистора не є критичним: зазвичай достатньо 10 кОм. Коли використовується для забезпечення «високого» (1) логічного рівня у випадку плаваючого джерела сигналу, цей резистор відомий як тяговий резистор:

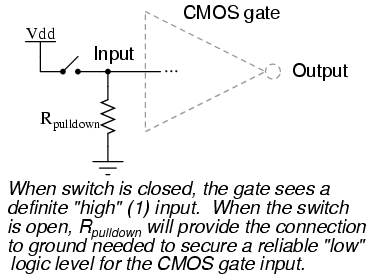

Коли такий резистор використовується для забезпечення «низького» (0) логічного рівня в разі плаваючого джерела сигналу, він відомий як випадає резистор. Знову ж таки, значення для випадає резистора не критично:

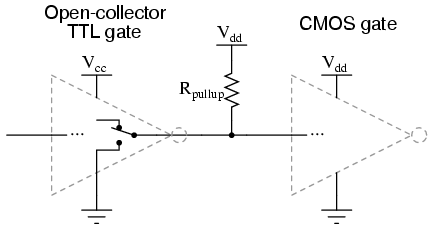

Оскільки виходи TTL з відкритим колектором завжди тонуть, ніколи не джерело, струм, підтягують резистори необхідні при сполученні такого виходу на вхід затвора CMOS:

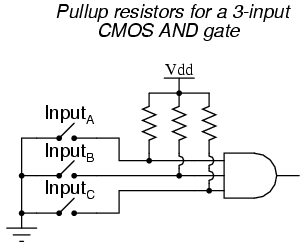

Хоча елементи CMOS, використовувані в попередніх прикладах, були всі інвертори (з одним входом), той же принцип тягнучих і висувних резисторів застосовується до багатовхідних CMOS воріт. Зрозуміло, для кожного входу затвора буде потрібно окремий тягне або висувний резистор:

Це підводить нас до наступного питання: як ми проектуємо CMOS ворота з кількома входами, такі як AND, NAND, OR та NOR? Не дивно, що відповідь (и) на це питання виявляють простоту конструкції, подібну до інвертора CMOS над його еквівалентом TTL.

CMOS NAND ворота

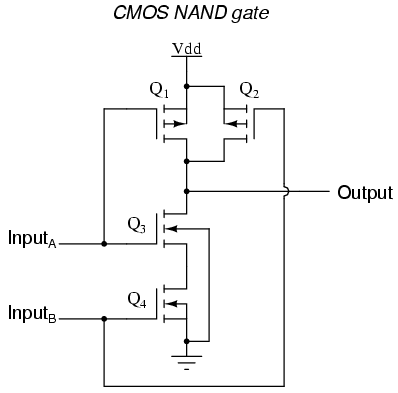

Наприклад, ось принципова схема для затвора CMOS NAND:

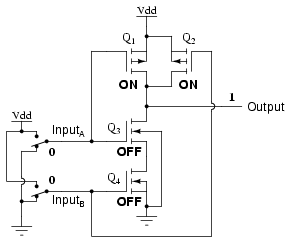

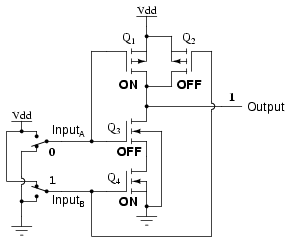

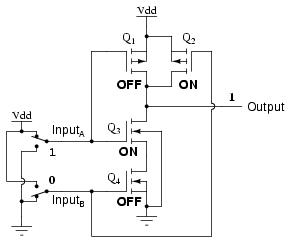

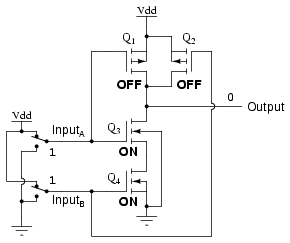

Зверніть увагу, як транзистори Q 1 і Q 3 нагадують послідовно з'єднану комплементарну пару з схеми інвертора. Обидва управляються одним і тим же вхідним сигналом (вхід А), вимкненням верхнього транзистора і включенням нижнього транзистора, коли вхід «високий» (1), і навпаки. Зверніть увагу також, як транзистори Q 2 і Q 4 аналогічно контролюються одним і тим же вхідним сигналом (вхід B), і як вони також будуть демонструвати однакову поведінку вкл/викл для тих же вхідних логічних рівнів. Верхні транзистори обох пар (Q 1 і Q 2) мають паралельні висновки джерела і зливу, тоді як нижні транзистори (Q 3 і Q 4) послідовно з'єднані. Що це означає, що вихід буде йти «високим» (1), якщо або верхній транзистор насичує, і буде йти «низьким» (0) тільки в тому випадку, якщо обидва нижніх транзистори насичують. Наступна послідовність ілюстрацій показує поведінку цього елемента NAND для всіх чотирьох можливостей вхідних логічних рівнів (00, 01, 10 і 11):

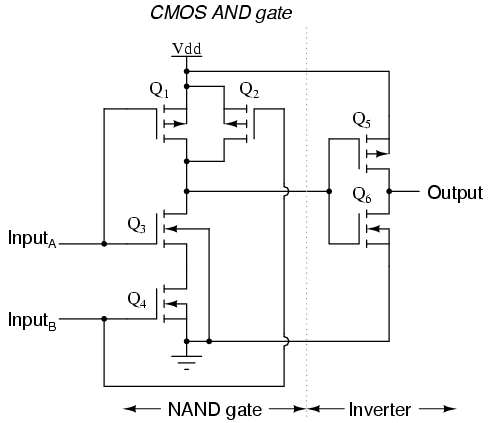

Як і у випадку з затвором TTL NAND, схема затвора CMOS NAND може бути використана в якості відправної точки для створення воріт І. Все, що потрібно додати, це ще один етап транзисторів для інвертування вихідного сигналу:

CMOS NOR Гейтс

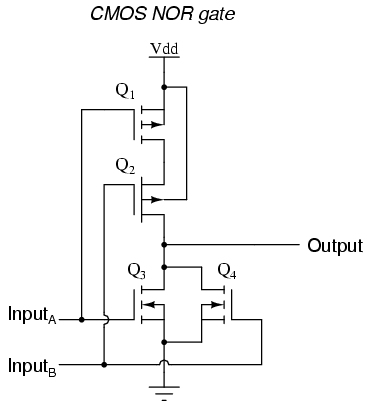

Схема затвора CMOS NOR використовує чотири МОП-транзистори так само, як затвор NAND, за винятком того, що його транзистори розташовані по-різному. Замість двох паралельних вихідних (верхніх) транзисторів, підключених до V dd, і двох послідовно з'єднаних потопаючих (нижніх) транзисторів, підключених до землі, NOR затвор використовує два послідовно з'єднаних вихідних транзисторів і два паралельно з'єднаних потопаючих транзисторів, як це:

Як і у випадку з затвором NAND, транзистори Q 1 і Q 3 працюють як додаткова пара, як і транзистори Q 2 і Q 4. Кожна пара управляється одним вхідним сигналом. Якщо вхід A або вхід B є «високими» (1), принаймні один з нижніх транзисторів (Q 3 або Q 4) буде насичений, що робить вихід «низьким» (0). Тільки в тому випадку, якщо обидва входи будуть «низькими» (0), обидва нижні транзистори будуть перебувати в режимі відключення, а обидва верхні транзистори будуть насиченими, умови, необхідні для виходу «високий» (1). Така поведінка, звичайно, визначає логічну функцію NOR.

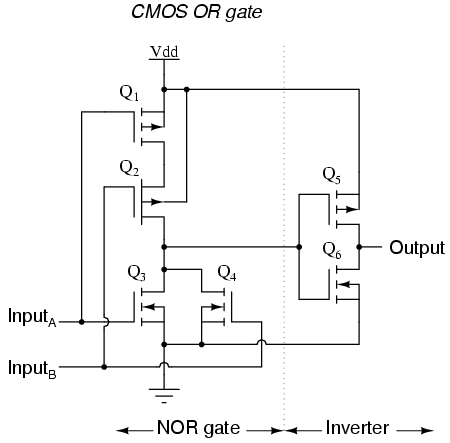

CMOS АБО ворота

Функція OR може бути побудована з базового затвора NOR з додаванням інверторного каскаду на виході:

TTL проти CMOS: переваги та недоліки

Оскільки здається, що будь-які ворота, які можна побудувати за допомогою технології TTL, можна дублювати в CMOS, чому ці дві «сім'ї» логічного дизайну все ще співіснують? Відповідь полягає в тому, що і TTL, і CMOS мають свої унікальні переваги.

В першу чергу в списку порівнянь між TTL і CMOS стоїть питання енергоспоживання. У цьому показі продуктивності CMOS є безперечним переможцем. Оскільки комплементарні P- і N-канальні MOSFET пари ланцюга затвора CMOS (в ідеалі) ніколи не проводять одночасно, є мало або немає струму, що проводиться ланцюгом від джерела живлення V dd, за винятком того, який струм необхідний для джерела струму до навантаження. TTL, з іншого боку, не може функціонувати без певного струму, проведеного в будь-який час, через вимоги до зміщення біполярних транзисторів, з яких він виготовлений.

Однак є застереження до цієї переваги. Хоча розсіювання потужності затвора TTL залишається досить постійним незалежно від його робочого стану (ів), CMOS затвор розсіює більше енергії, оскільки частота його вхідного сигналу (ів) зростає. Якщо CMOS затвор працює в статичному (незмінному) стані, він розсіює нульову потужність (в ідеалі). Однак схеми затвора CMOS проводять перехідний струм під час кожного перемикача вихідного стану від «низького» до «високого» і навпаки. Так, чим частіше CMOS затвор перемикає режими, тим частіше він буде тягнути струм від живлення V dd, отже, більше розсіювання потужності на більших частотах.

CMOS-затвор також витягує набагато менше струму від виходу воріт, ніж затвор TTL, оскільки MOSFET - це пристрої, керовані напругою, а не контрольовані струмом. Це означає, що один затвор може керувати набагато більше входів CMOS, ніж входи TTL. Міра того, скільки входів затвора може керувати одним виходом затвора, називається розгалуженням.

Ще однією перевагою, якою користуються конструкції воріт CMOS над TTL, є набагато ширший допустимий діапазон напруг живлення. У той час як TTL ворота обмежені напругою живлення (V cc) від 4,75 до 5,25 вольт, CMOS ворота, як правило, здатні працювати на будь-якій напрузі від 3 до 15 вольт! Причиною цієї нерівності в напругах живлення є відповідні вимоги зміщення MOSFET проти біполярних транзисторів переходу. МОП-транзистори управляються виключно напругою затвора (щодо підкладки), тоді як BJT - пристрої, керовані струмом. Опір ланцюга затвора TTL точно розраховані для належних струмів зміщення, припускаючи 5 вольт регульованого джерела живлення. Будь-які значні зміни в цій напрузі джерела живлення призведуть до того, що струми зміщення транзистора будуть неправильними, що потім призводить до ненадійної (непередбачуваної) роботи. Єдиний ефект, який зміни напруги живлення мають на затвор CMOS, - це визначення напруги «високого» (1) стану. Для CMOS затвора, що працює на напрузі живлення 15 вольт (V dd), вхідний сигнал повинен бути близьким до 15 вольт, щоб вважатися «високим» (1). Поріг напруги для «низького» (0) сигналу залишається колишнім: близько 0 вольт.

Одним з вирішених недоліків CMOS є повільна швидкість, в порівнянні з TTL. Вхідні ємності CMOS затвора набагато, набагато більше, ніж у порівнянного TTL-шлюзу - завдяки використанню MOSFET, а не BJTS, і тому CMOS ворота будуть повільніше реагувати на перехід сигналу (низько-високий або навпаки), ніж затвор TTL, всі інші фактори рівні. Константа часу RC, утворена опорами ланцюга та вхідною ємністю затвора, як правило, перешкоджають швидкому зростанню та падінню цифрового логічного рівня, тим самим погіршуючи продуктивність високої частоти.

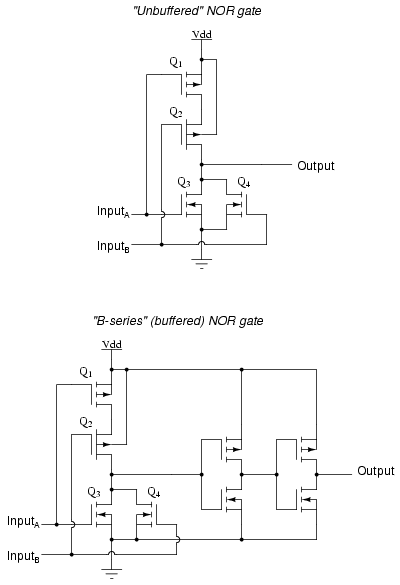

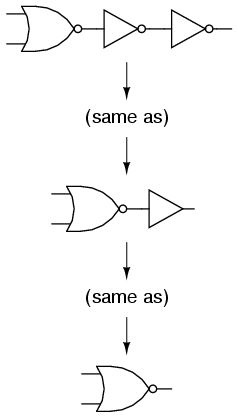

Стратегія мінімізації цього властивого недоліку схеми затвора CMOS полягає в «буфері» вихідного сигналу додатковими транзисторними каскадами, щоб збільшити загальний коефіцієнт посилення напруги пристрою. Це забезпечує більш швидку перехідну вихідну напругу (від високого до низького або низького до високого) для вхідної напруги, що повільно змінюється від одного логічного стану до іншого. Розглянемо цей приклад «небуферизованих» воріт NOR проти «буферного» або B-серії, NOR воріт:

По суті, вдосконалення конструкції серії B додає два інвертори на вихід простої схеми NOR. Це не має мети, що стосується цифрової логіки, оскільки два каскадних інвертора просто скасовують:

Однак додавання цих інверторних ступенів до схеми дійсно служить меті збільшення загального посилення напруги, роблячи вихід більш чутливим до змін у вхідному стані, працюючи над подоланням властивої повільності, викликаної вхідною ємністю CMOS затвора.

Рецензія

- Логічні вентилі CMOS виготовляються з транзисторів IGFET (MOSFET), а не з біполярних транзисторів.

- Входи CMOS затвора чутливі до статичної електрики. Вони можуть бути пошкоджені високими напругами, і вони можуть припускати будь-який логічний рівень, якщо залишити плаваючим.

- Підтягуючі та висувні резистори використовуються для запобігання плаванню входу затвора CMOS, якщо він приводиться в рух джерелом сигналу, здатним лише джерелом або потоком.

- CMOS ворота розсіюють набагато меншу потужність, ніж еквівалентні TTL ворота, але їх розсіювання потужності збільшується з частотою сигналу, тоді як розсіювання потужності затвора TTL приблизно постійна в широкому діапазоні умов експлуатації.

- Входи затвора CMOS отримують набагато менше струму, ніж входи TTL, оскільки МОП-транзистори - це пристрої, керовані напругою, а не контрольовані струмом.

- CMOS ворота здатні працювати на набагато ширшому діапазоні напруг живлення, ніж TTL: як правило, від 3 до 15 вольт проти 4,75 до 5,25 вольт для TTL.

- CMOS ворота, як правило, мають набагато нижчу максимальну робочу частоту, ніж TTL ворота через вхідні ємності, викликані MOSFET воріт.

- CMOS ворота серії B мають «буферні» виходи для збільшення посилення напруги від входу до виходу, що призводить до більш швидкої вихідної реакції на зміни вхідного сигналу. Це допомагає подолати властиву повільність CMOS воріт через вхідну ємність MOSFET і постійну часу RC тим самим породив.