3.10: Логіка CMOS

- Page ID

- 34474

Розглянемо наступне, показане на малюнку\(\PageIndex{1}\).

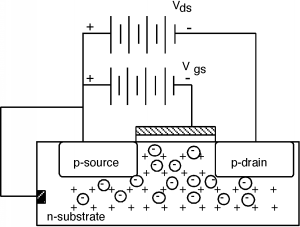

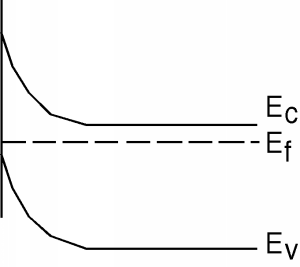

Це дуже схоже на наш попередній MOSFET, за винятком того, що тепер у нас є підкладка n-типу, а джерела та стоку області p-типу. Якщо застосувати негативний\(V_{\text{gs}}\) (з джерелом, з'єднаним з підкладкою n-типу), то індукований негативний заряд на затворі буде відганяти електрони, а якщо смуги під затвором досить зігнуті вгору, утворюють інверсійний шар дірок (див. Рис\(\PageIndex{2}\),. роблячи режим посилення p-канального MOSFET, або PMOS транзистора. (На відміну від NMOS транзистора, який ми вивчали спочатку.). Зверніть увагу, що у PMOS-транзистора буде негативний\(V_{T}\). Тобто напруга затвора має бути менше напруги джерела/підкладки, щоб включити пристрій. Чим більше негативних,\(V_{\text{gs}}\) тим більше струму у нас буде протікати через пристрій.

Виходить, що поєднання як n-канального, так і p-канального пристрою на одній схемі може бути дуже вигідною. Така технологія називається CMOS, для «комплементарних МОП». Ось як ми використовуємо p-канальний транзистор в ланцюзі інвертора.

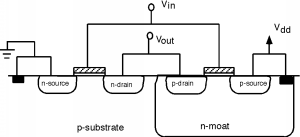

Перш за все, однак, ми повинні побачити, як би ми його зробили. Існує принципова проблема в спробі використовувати як n-канальні, так і p-канальні пристрої в одній схемі. Що це таке? Здавалося б, нам потрібні два різних види підкладок, як підкладка p-типу для n-канального транзистора, так і підкладка n-типу для пристрою p-каналу. Існує спосіб обійти цю проблему, зробивши те, що називається танком або ровом. Рів - це відносно глибока область одного виду матеріалу, поміщеного в підкладку-господар протилежного типу (рис.\(\PageIndex{3}\)). Ми можемо помістити регіони джерела/зливу n-типу в р-субстрат і р-типу джерело/дренажні регіони в n-рів. На малюнку\(\PageIndex{4}\) ми також покажемо вентилі, і як весь інвертор з'єднаний між собою.

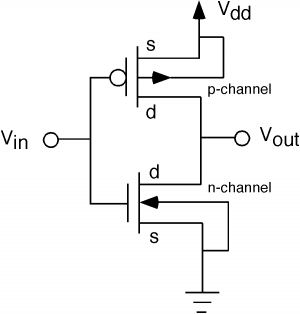

Тепер давайте намалюємо схему: пристрій p-каналу малюється так само, як n-канальний пристрій, за винятком того, що ми ставимо трохи «міхура» на ворота, щоб означати, що це MOSFET іншого кольору. Хоча ми зазвичай не робимо цього постійно, ми також показали з'єднання підкладки на цій схемі. Ці з'єднання показують, що MOSFET - це принаймні чотиритермінальний пристрій, а не тритермінальний, як люди часто припускають. Оскільки в p-канальному пристрої підкладка має n-тип, ми показуємо з'єднання підкладки як спрямовану назовні стрілку. Підкладка p-типу для n-канального пристрою показана у вигляді спрямованої всередину стрілки. N-канальна підкладка з'єднана з землею, а підкладка p-каналу з'єднана з\(V_{\text{dd}}\). Зверніть увагу, що оскільки n-рів знаходиться в,\(V_{\text{dd}}\) а p-підкладка знаходиться на землі, рв-підкладка p-n перехід зворотно зміщений, і тому між ними не повинен протікати струм.

Зазвичай ми також не маркуємо джерело і зливаємо, але ми робимо тут, лише для повноти. Відзначимо, що на відміну від біполярного транзистора, транзистор є воістину симетричним пристроєм. Дійсно немає можливості сказати джерело зі стоку. За умовністю ми називаємо елемент, який з'єднаний з підкладкою (або ровом) джерелом, а інший - стоком. Іноді ви почуєте область під воротами (субстратом або ровом), яку називають заднім тілом.

Тепер подивимося, як працює ця схема. Якщо\(V_{\text{in}}\) високий (на або поблизу\(V_{\text{dd}}\)) NMOS транзистор буде включений. Напруга між затвором і підкладкою p-канального пристрою знаходиться на нулі або близько. \(V_{\text{dd}}\)Ворота на і так рів! Звідси верхній транзистор буде вимкнений. Вихід, таким чином, буде низьким.

Якщо вхідна напруга знаходиться на землі або поблизу неї («низький»), то n-канальний пристрій відключається. Напруга між затвором і підкладкою пристрою p-каналу тепер\(\simeq \left( -V_{\text{dd}} \right)\). (\(\simeq 0\)Ворота є, а підкладка знаходиться в\(V_{\text{dd}}\).) Якщо PMOS-транзистор має порогове напруга\(V_{T}\)\(-2 \mathrm{~V}\), скажімо, то він включиться і вихід буде високим. Однак зверніть увагу, що в будь-якому стані, високому або низькому, немає статичного струму, що протікає через інвертор.

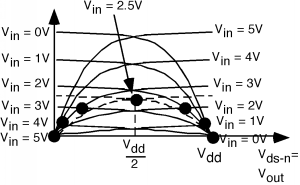

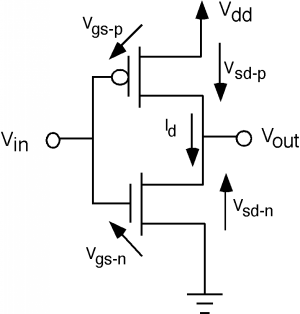

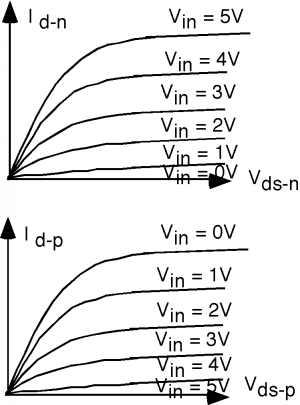

Трансферні характеристики для цієї схеми трохи складніше. По-перше, давайте переконаємося, що у нас визначені наші напруги та струми. З малюнка\(\PageIndex{6}\), n-канальний затвор-джерело напруги\(V_{\text{gs-}n}\), є справедливим\(V_{\text{in}}\). Напруга затвор-джерело для пристрою p-каналу,\(V_{\text{gs-}p}\), є\(V_{\text{in}} - V_{\text{dd}\);\(V_{\text{ds-}p}\), напруга сток-джерело для транзистора p-каналу можна записати як\(V_{\text{ds-}n} - V_{\text{dd}}\). Для поточних,\(I_{d \text{-} n} = I_{d \text{-} p} = I_{d}\). Як видно на малюнку\(\PageIndex{7}\), у нас є два набори характерних кривих. Відзначимо\(V_{\text{gs-}p} = V_{\text{in}} - V_{\text{dd}}\), що з тих пір\(V_{\text{in}} = 0 \mathrm{~V}\), коли\(V_{\text{gs-}p} = -5 \mathrm{~V}\) і так сильно включений транзистор.

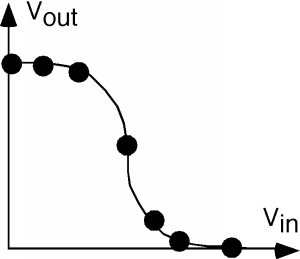

У цьому випадку у нас є ряд різних «ліній навантаження», тому що для кожної\(V_{\text{in}}\) ми маємо різну криву як для n-, так і для p-канальних транзисторів. Це показано на малюнку\(\PageIndex{8}\). Чорні плями показують точку перетину. Дотримуйтесь кількох кривих уздовж, щоб побачити, чи згодні ви з тим, де були розміщені плями. Ми також додали пару пунктирних кривих,\(V_{\text{in}} = 2.5 \mathrm{~V}\) щоб ми могли отримати точку «перевертання». Проектування розташування чорних крапок на\(V_{\text{ds-}n}\) (або\(V_{\text{out}}\)) вісь дасть нам значення\(V_{\text{out}}\) для кожного з вхідних напруг,\(V_{\text{in}}\). Отримана крива показана на малюнку\(\PageIndex{9}\). Це дає нам гарне «відчуття» того, як працює інвертор, і як змінюється вихід у залежності від входу. Відзначимо, що ця крива передачі досить симетрична близько 2,5 вольт, і йде весь шлях від +5 до 0 вольт на виході.